[전자계산기] 조합 논리 회로(Combinational Logic Circuit)

조합 논리 회로

논리 게이트의 조합으로 만들어지는 회로로 현재의 입력에 의해서만 출력이 결정되는 회로를 의미

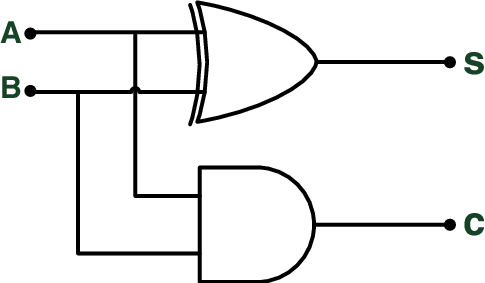

반가산기(Half Adder)

2개의 2진 입력 변수 A와 B를 더한 합 S(Sum)와 자리 올림 수 C(Carry)를 얻는 회로

하나의 AND 게이트와 XOR(eXclusive OR) 게이트를 조합해서 구성

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

합(Sum) : S = A·B + A·B = A ⊕ B

캐리(Carry) : C = A · B

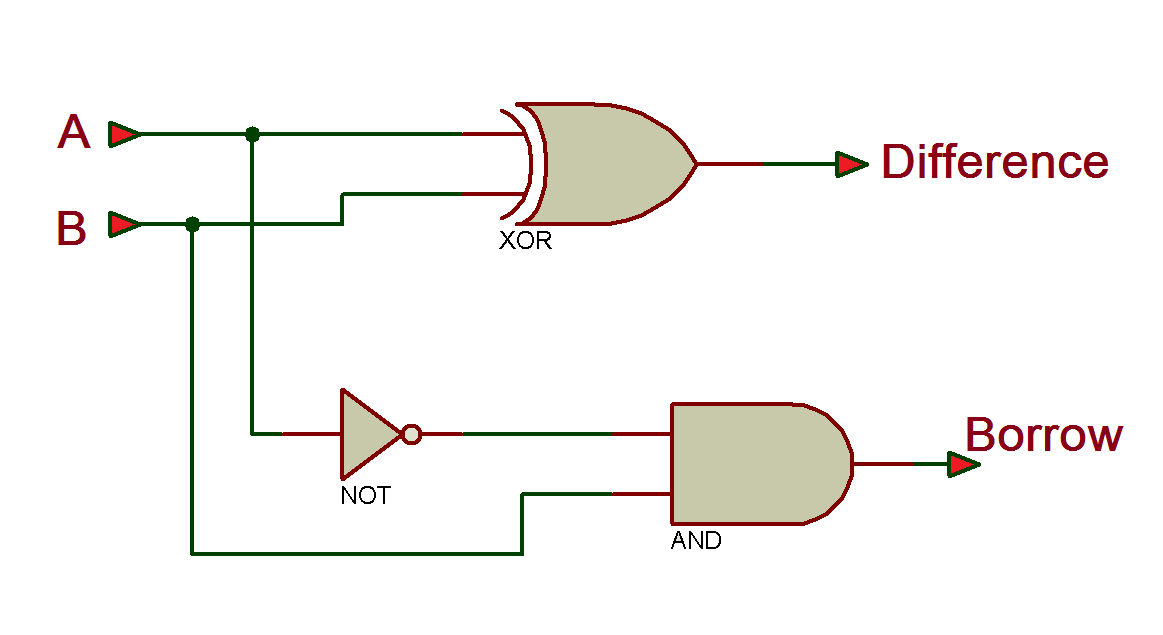

반감산기(Half Subtracter)

2개의 2진 입력 변수 X에서 Y를 뺀 차 D와 빌려온 수(자리 내림 수) B를 얻는 회로

하나의 NOT 게이트 및 AND 게이트와 XOR 게이트를 조합해서 구성

| X | Y | D | B |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

차(Difference) : D = X·Y + X·Y = X ⊕ Y

빌려온 수(자리 내림, Borrow) : B = X · Y

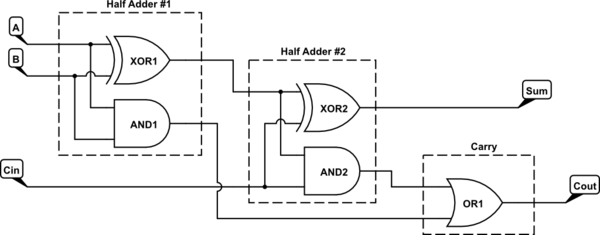

전가산기(Full Adder)

2진수 가산을 완전히 하기 위하여 아래 자리로부터 자리 올림된 수도 고려하여 3개의 2진수를 더할 수 있게 만든 회로

반가산기 2개와 OR 게이트 1개를 연결하여 구성

| A | B | C | S | C0 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

합(Sum) : S = A⊕B⊕C

캐리(Carry) : C0 = (A⊕B)·C + A·B = A·B + B·C + A·C

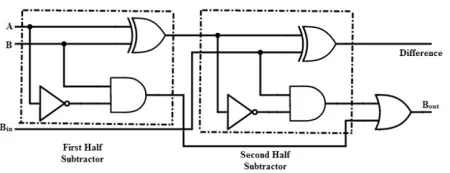

전감산기(Full Subtracter)

2진수 감산을 완전히 하기 위하여 아래 자리로부터 자리 내림수도 고려하여 3개의 2진수를 감산할 수 있게 만든 회로

반감산기 2개와 OR 게이트 1개를 연결하여 구성

| X | Y | B | D | B1 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

차(Difference) : D = X⊕Y⊕B

빌려온 수(Borrow) : B1 = (X⊕Y)·B + X·Y

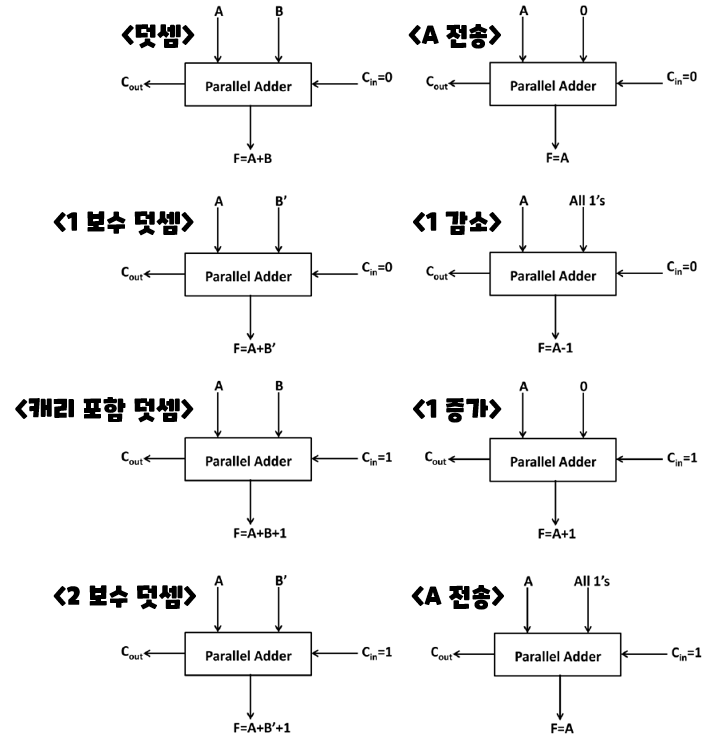

병렬 가산기(Parallel Adder)

여러 비트를 가산하기 위한 회로

반가산기 또는 전가산기를 여러 개 합쳐서 만들어진다

- 전가산기로 구성하여 N비트 병렬 가산기를 만들 경우

N개의 전가산기 필요 - 반가산기로 구성하여 N비트 병렬 가산기를 만들 경우

(2N-1)개의 반가산기와(N-1)개의 OR 게이트 필요

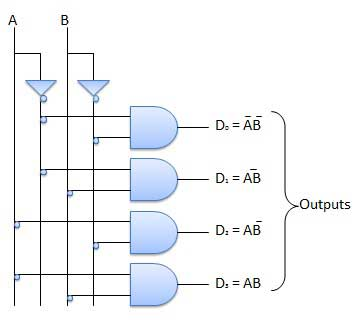

디코더(Decoder)

컴퓨터 내부에서 2진수로 코드화된 데이터를 해독하여 대응되는 한 개의 신호로 바꿔주기 때문에 해독기라고도 한다

N개의 입력으로 최대 2N개의 출력을 얻을 수 있다

AND 게이트로 만들어진다

| A | B | D0 | D1 | D2 | D3 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

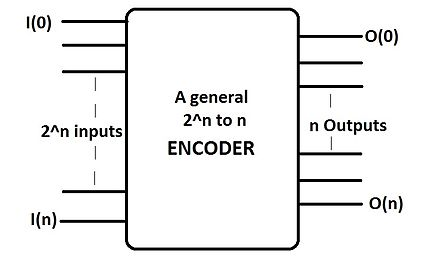

인코더(Encoder)

입력 정보를 여러 자리의 2진수로 코드화하여 전달하는 회로

해독기와 정반대의 동작을 수행

2N개의 입력을 받아 N개를 출력

| 입력 | D0 | D1 | D2 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 |

| 2 | 0 | 1 | 1 |

| 3 | 1 | 0 | 1 |

| 4 | 0 | 1 | 0 |

| 5 | 1 | 0 | 0 |

| 6 | 0 | 0 | 0 |

| 7 | 1 | 1 | 1 |

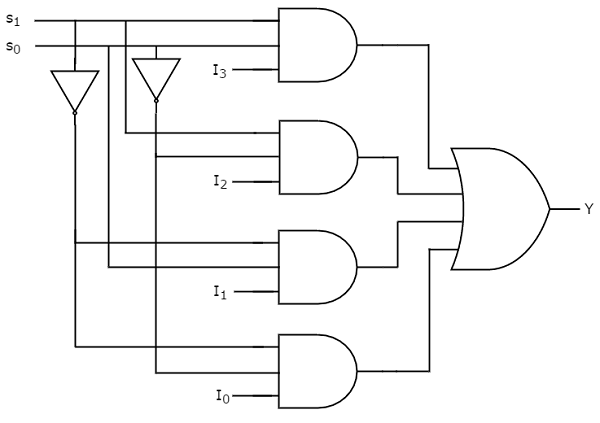

멀티플렉서(Multiplexer)

2N개의 입력선에서 N개의 선택선을 가지고 하나의 출력을 얻도록 구성

여러 개의 입력 회선이 들어가서 하나의 특정 회선을 선택하도록 하므로 선택기라고도 한다

공통적인 버스 라인을 구성하는데 많이 사용

| S0 | S1 | Y선택 회선 |

|---|---|---|

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | I3 |

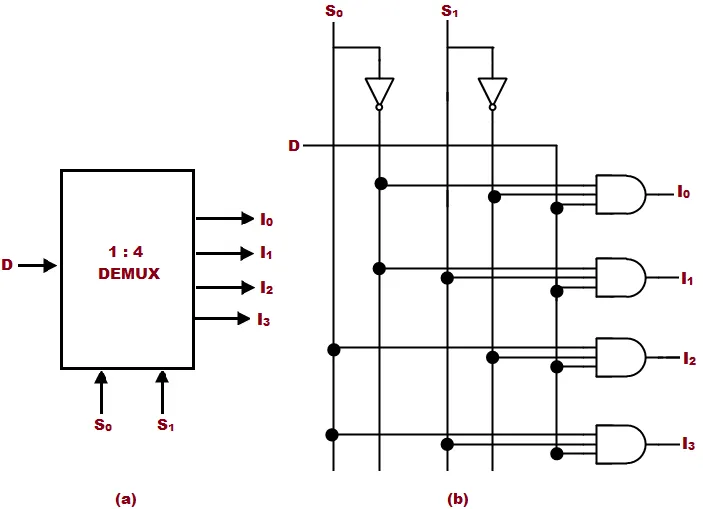

디멀티플렉서(Demultiplexer)

하나의 입력 정보를 N개의 선택선을 가지고 2N개의 출력을 얻도록 구성

중앙 처리 장치에서 어떤 내용을 특정 장치로 출력시킬 때 많이 사용

| S0 | S1 | D0 | D1 | D2 | D3 |

|---|---|---|---|---|---|

| 0 | 0 | I | 0 | 0 | 0 |

| 0 | 1 | 0 | I | 0 | 0 |

| 1 | 0 | 0 | 0 | I | 0 |

| 1 | 1 | 0 | 0 | 0 | I |

비교기(Comparator)

논리적으로 두 수를 비교한다면 ‘같다’, ‘같지 않다’만 판별하면 되므로 두 수 A, B를 XNOR 게이트로 연결하여 1이 얻어지면 ‘같다’고 판별할 수 있다

N비트 논리 비교기를 만들기 위해서는 XNOR 게이트 N개가 필요

3-상태 버퍼(Tri-State Buffer)

3가지 상태 중

1의 상태는 전기적으로 하이 레벨(H)

0의 상태는 로우 레벨(L)

또 다른 상태는 고 임피던스(회로가 끊어진 상태) 상태를 의미한다.

3-상태 버퍼 회로는 인에이블(1) 또는 디스에이블(0) 단자에 의하여 데이터의 전송 방향을 하드웨어적으로 제어하는 데 사용

댓글남기기