[전자계산기] 가상 기억 장치 및 인터리빙

가상 기억 장치(Virual Memory)

기억 용량을 효과적으로 이용하기 위하여 주기억 장치보다 훨씬 큰 보조 기억 공간을 주기억 장치의 연속된 기억 공간으로 사용하는 방식

- 주소 공간의 확대가 목적

- 보조 공간 전체를 주소 공간으로 보고 명령어를 만드는 방식

- 소프트웨어로 실현

- 보조 기억 장치는 직접 접근 장치(DASD)여야 한다(자기 디스크)

- 가상 주소를 실제 주소로 변환하는 과정이 필요

-

사상(Mapping)

가상 기억 장치에 있는 내용을 어떤 일정한 단위로 분류하여 이 단위의 내용이 실기억 장치의 어느 위치에 있는지를 알아내는 방법 -

페이징(Paging)

사상 기억 장치에 있는 내용을 어떤 일정한 단위로 분류할 때 분류 단위가 똑같은 크기일 때를 페이징이라 한다 -

세그먼트(Segment)

가상 기억 장치에 있는 내용을 어떤 일정한 단위로 분류할 때 분류 단위가 같지 않은 경우를 세그먼트라 한다 -

페이지 폴트(Page Fault)

주기억 장치에 없는 페이지가 참조될 때 생기는 인터럽트로, 페이지 폴트가 발생하면 CPU가 하던 일을 중단하고 해당 페이지를 주기억 장치로 옮겨 놓은 후 다시 인터럽트 처리를 하게 된다 -

스태깅(Staging)

가상 기억 체제에서 페이지 폴트가 발생하면 희생 페이지를 결정해서 보조 기억 장치의 이전 위치에 기억시키고 새로운 페이지를 이전 희생된 페이지가 있던 곳에 위치시키는 과정을 의미 -

스래싱(Thrashing)

보조 기억 장치의 페이지 접근 횟수가 많아 작업 수행 시간보다 페이징 교체 시간이 많아지는 경우

관리 기법

-

연속 로딩 기법

프로그램을 연속된 기억 장소에 저장하여 수행하는 기법으로 처음부터 구역을 분할해 두는 고정 분할과 필요에 따라 구역을 정하는 동적 분할이 있다 -

분산 로딩 기법

프로그램을 적당한 크기로 나누어 필요한 부분만 주기억 장치에 저장하여 수행하는 기법으로 주소 공간과 실제 공간을 분리하여 사용한다. 보조 기억 장치의 페이지 접근 횟수가 많아 작업 수행 시간보다 페이지 교체 시간이 많다 -

페이징

프로그램을 비연속적인 기억 공간에 적재하여 수행할 수 있도록 실기억 공간과 가상 기억 공간을 균등 분할하고 매핑 테이블을 이용하여 가상 주소를 실 주소로 변환하는 방법으로 외부 단편화가 발생하지 않는다 -

세그먼트

프로그램을 주프로그램, 부프로그램, 배열, 스택 등 용도가 다른 여러 크기의 세그먼트로 나누어 수행시키는 방법으로 외부 단편화가 발생할 수 있다

페이지 교체 알고리즘

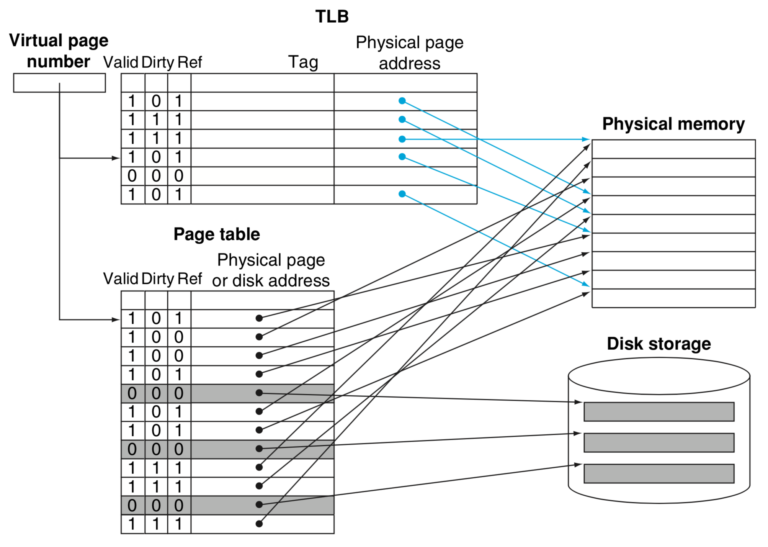

TLB

변환 색인 버퍼(Translation Lookaside Buffer, TLB)는 가상 메모리 주소를 물리적인 주소로 변환하는 속도를 향상시키기 위해 MMU에서 사용하는 고속 캐시로 최근에 일어난 가상 메모리 주소와 물리 주소의 변환 테이블을 저장하기 때문에 일종의 주소 변환 캐시라고 할 수 있다

TLB는 CPU와 CPU 캐시 사이, CPU 캐시와 메인 메모리 사이 등 여러가지 다른 레벨의 캐시들 사이에서 주소를 변환하는데 사용할 수 있다

메모리 인터리빙

메모리 인터리빙 기법은 인접한 메모리 위치를 서로 다른 메모리 뱅크(Bank)에 둠으로써 동시에 여러 곳을 접근할 수 있게 하는 것으로 CPU의 처리 속도에 비해 사이클 타임이 오래 걸리지만 기억 장치에 접근하는 시간을 효율적으로 높일 수 있는 방법

- 캐시 기억 장치, 고속 DMA(Direct Memory Access) 전송 등에서 주로 사용

- CPU가 시분할하여 여러 모듈을 번갈아가면서 접근

- 중앙 처리 장치의 쉬는 시간을 줄일 수 있다

- 단위 시간 당 수행할 수 있는 명령어의 수를 증가시킬 수 있다

- 이 기억 장치를 구성하는 모듈의 수만큼 단어들에 동시 접근이 가능

- 기억 장치 버스를 시분할하여 사용

종류

- 상위 인터리빙(High-Order Interleaving)

메모리 주소의 상위 비트들에 의해 모듈이 선택되고, 하위 비트들은 각 모듈 내의 기억 장소의 주소를 나타낸다- 한 모듈에서 에러가 발생해도 해당 모듈만 영향을 받는다

- 동시 접근을 통한 성능 향상의 어려움 존재

- 하위 인터리빙(Low-Order Interleaving)

하위 비트들에 의해 모듈이 선택되고, 상위 비트들은 각 모듈 내의 주소를 나타낸다- 다수의 모듈이 동시에 동작 가능

- 새로운 메모리 뱅크 추가 시 전체에 영향을 준다

- 혼합 인터리빙(High-Low-Order Interleaving)

기억장치 모듈을 뱅크로 그룹화하고 각 그룹 내에서 하위 인터리빙 수행- 상위, 하위 인터리빙의 단점 해결

- 구현이 복잡하고 어려움

엑세스 방식

- C-Access 방식

- 주소들이 프로세서-기억 장치간 버스를 통해 순차적으로 기억 장치 모듈에 도착

- 모듈들에서의 엑세스 동작들이 시간적으로 중첩되지만 실제 엑세스 시간은 약간씩 다르다

- 이 때 주소들이 버스를 통해 각 기억 장치 모듈들로 전송되는 과정에서 버스의 경합으로 일정 시간 간격으로 주소들이 각 모듈에 도착하지 못할 수 있다. 이럴 경우 읽기 동작의 동시성이 줄어들고 결과적으로 데이터 전송도 연속적으로 이루어지지 못하게 된다

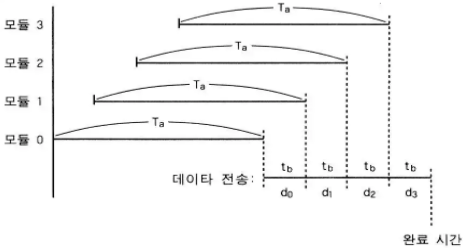

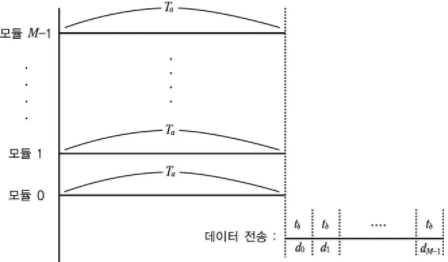

- S-Access 방식

액세스 시간 : T = Ta + (M × tb)

Ta: 기억 장치 액세스 시간, tb: 버스 클럭의 주기, M: 기억 장치 모듈의 수- 모든 기억 장치 모듈들에서 읽기 동작들이 동시에 시작되도록 하고, 읽혀진 데이터들을 순차적으로 전송

- DDR DRAM 등에 적용되고 있으며 연속적인 입력 데이터 흐름이 필요한 파이프라인 컴퓨터에서 주로 사용

댓글남기기