[전자계산기] 순서 논리 회로(Sequential Logic Circuit)

순서 논리 회로

기억 능력을 갖추면서 입력과 내부 상태의 조합에 의해 출력이 결정되는 회로

플립플롭이나 레지스터 장치로 구성된다

플립플롭(Flip-Flop)

순서 논리 회로를 구성하는 기본 기억 소자로 1비트를 기억할 수 있는 2진 Cell을 의미

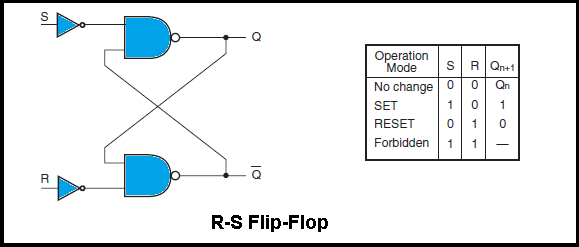

RS 플립플롭

보통 NAND 게이트를 이용해서 구성

SET(S) 단자와 RESET(R) 단자를 갖으며, 모두 1인 경우는 허용되지 않는다

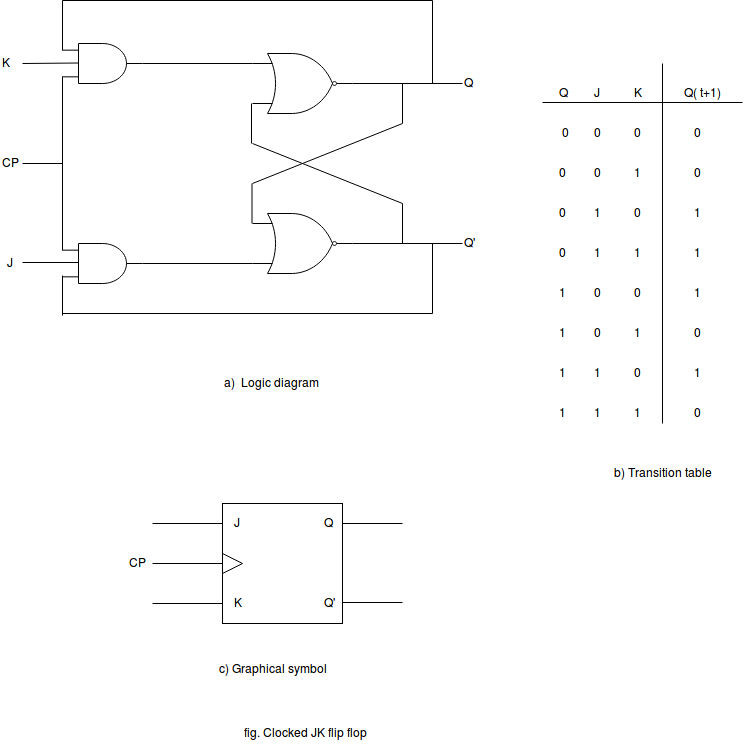

JK 플립플롭

RS 플립플롭에서 S와 R이 모두 1일 때 허용되지 않는 것을 보완해서 이것이 허용되도록 고안된 플립플롭

RS 플립플롭의 내부 상태와 입력 상태를 AND 게이트로 처리하여 입력하는 플립플롭

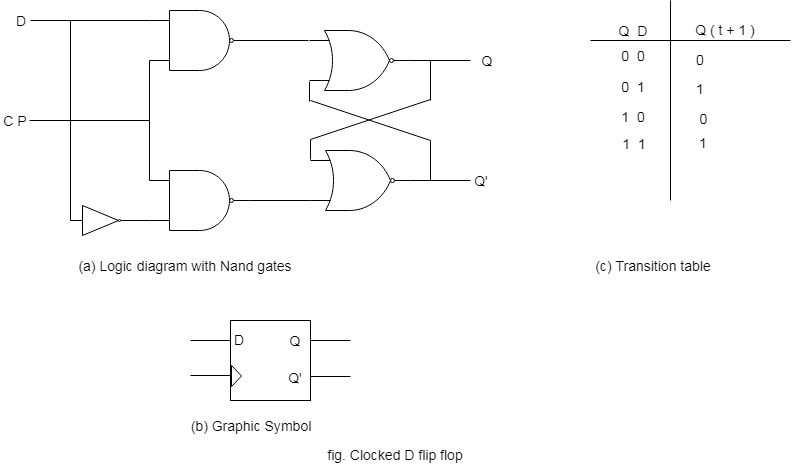

D 플립플롭

RS나 JK 플립플롭에서 서로 베타적인 경우만 이용되도록 고안된 플립플롭, 1비트 지연 소자로 사용된다

(S가 0이면 R은 1, S가 1이면 R은 0)

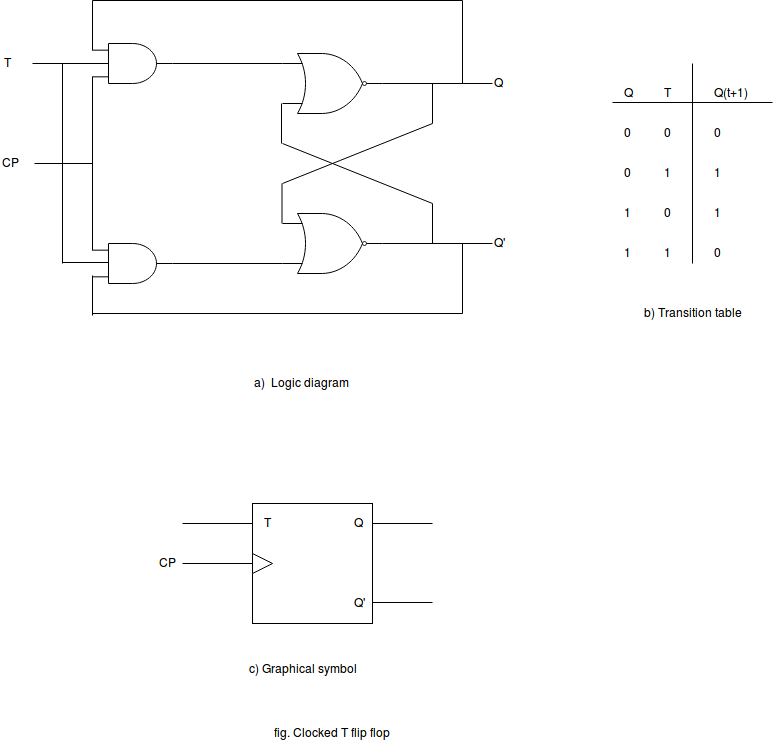

T 플립플롭

JK 플립플롭에서 J, K가 같은 값이 입력될 때만 이용할 수 있도록 고안된 플립플롭, 토글(Toggle) 기능을 이용하고자 할 때 사용된다

(J가 0이면 K는 0, J가 1이면 K는 1)

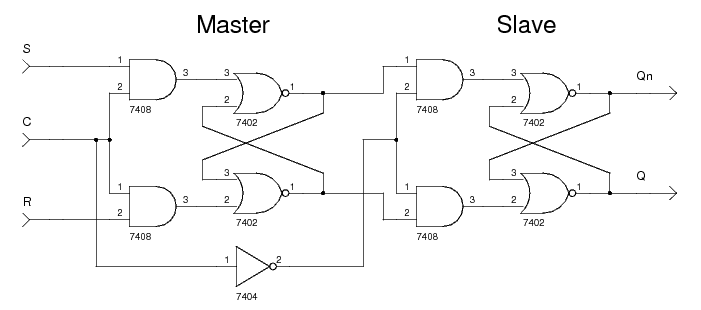

마스터 슬레이브(Master-Slave, 주종) 플립플롭

Race 현상을 해결하기 위해 고안된 플립플롭

Race 현상 : 출력이 입력에 피드백되어 플립플롭의 내부 상태가 변화되면 출력 상태가 변할 때 입력도 변하게 되므로 오동작이 발생하게 되는 현상

하나의 플립플롭(주 플립플롭)이 주인 역할을 하고, 다른 하나의 플립플롭(종 플립플롭)이 종속되어 동작하도록 두 개 이상의 플립플롭 회로를 결합한 것

주 플립플롭은 시간 펄스가 상승할 때 동작하고, 종 플립플롭은 시간 펄스가 하강할 때 동작

카운터(Counter)

시간 펄스의 수를 카운트하거나 제어 장치에서 각종 회로의 동작을 제어하는데 사용

-

리플 카운터(Ripple Counter)

가장 기본이 되는 비동기형(Asynchronous) 카운터. 플립플롭의 수를 n이라 할 때, 2n개까지의 독립된 수 전부를 표현 -

모드 카운터(MOD Counter)

N개의 서로 다른 출력상태를 갖는 카운터. N개의 서로 다른 출력상태를 나타낸 후 다시 원래의 상태로 복귀해 다시 N개의 출력상태를 반복

레지스터(Register)

연산에 사용될 데이터가 대기하거나 연산된 결과데이터가 임시적으로 대기

-

시프트 레지스터(Shift Register)

현재 레지스터에 있는 내용을 왼쪽이나 오른쪽의 연결된 플립플롭을 1비트씩 이동시켜 밀어내기와 같은 동작을 수행하는 레지스터 -

병렬 시프트 레지스터(Parallel Shift Register)

N개의 비트로 구성된 레지스터의 내용을 연결된 다른 레지스터로 한 번에 이동시킬 수 있는 레지스터

댓글남기기